WDC reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. Information contained herein is provided gratuitously and without liability, to any user. Reasonable efforts have been made to verify the accuracy of the information but no guarantee whatsoever is given as to the accuracy or as to its applicability to particular uses. In every instance, it must be the responsibility of the user to determine the suitability of the products for each application. WDC products are not authorized for use as critical components in life support devices or systems. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties. The sale of any WDC product is subject to all WDC Terms and Conditions of Sales and Sales Policies, copies of which are available upon request.

Copyright (C) 1981-2009 by The Western Design Center, Inc. All rights reserved, including the right of reproduction in whole or in part in any form.

## 1.1 DOCUMENT REVISION HISTORY

| Version | Date     | Author     | Description              |

|---------|----------|------------|--------------------------|

| 1.0     | 12/02/09 | David Gray | Initial Document Release |

|         |          |            |                          |

|         |          |            |                          |

|         |          |            |                          |

|         |          |            |                          |

|         |          |            |                          |

|         |          |            |                          |

|         |          |            |                          |

## W65C02SPMCU Datasheet

#### 1.2 INTRODUCTION

The W65C02SPMCU Terbium Developer Kit (TDK) is a minimal System on Programmable Chip example based on WDC's Verilog IP Cores. This controller uses the W65C02SRTL as the processor and provides the user with a complete kit to begin application development and familiarization with the 65xx technology family. This controller was designed for WDC's Terbi-ECP2Mulator and is part of the Terbium Developer Kit (TDK). This board features a Lattice ECP2M50. A separate user guide is available for the Terbi-ECP2Mulator.

The software platform of the TDK is made up an easy to customize embedded monitor and WDC's ProSDK Tool Suite. The monitor provides in-circuit debug capabilities tethering the features of the hardware and ProSDK. The ProSDK Tool Suite provides all of the application development tools needed including: IDE, Instruction Set Simulator, Debugger, Assemblers, ANSI/ISO Standard Compilers, Optimizers, Linker, Symbol Tool, and Librarian.

#### KEY FEATURES OF THE W65C02SPMCU

- W65C02SRTL Microprocessor Core

- 32K x 8 FlashROM on chip

- 32K x 8 SRAM on chip

- General Purpose IO modules (2 used for Parallel TIDE Port Interface, 2 for USB TIDE Port Interface, 1 for LEDs Interface, 2 for Dual 7-Segment LED, 1 for User pushbuttons and HEX Input)

- Programmable Hardware Breakpoint for added in-circuit debug

- ProSDK Tool Suite for 65xx Assembly/ANSI/ISO Standard C application development

## W65C02SPMCU Datasheet

#### **MEMORY MAP**

| Start  | End    | Size    | Description                                |

|--------|--------|---------|--------------------------------------------|

| 0x8000 | OxFFFF | 32 KB   | 32KB Internal ROM                          |

| 0x7F00 | 0x7FFF | 256 B   | 256 Byte SRAM Used by WDC Monitor          |

| 0x7EFA | 0x7EFF | 6 B     | 6 Bytes Shadow Vectors Used by WDC Monitor |

| 0x7E80 | 0x7EF9 | 122 B   | 122 Bytes RAM Reserved for WDC Monitor     |

| 0x7E30 | 0x7E7F | 80 B    | 80 Bytes Reserved for IO                   |

| 0x7E2C | 0x7E2F | 4 B     | GPIO7 Registers (Pushbuttons and Hex)      |

| 0x7E28 | 0x7E2B | 4 B     | GPIO6 Registers (LEDs)                     |

| 0x7E24 | 0x7E27 | 4 B     | GPIO5 Registers (USB-TIDE CTRL Reg)        |

| 0x7E20 | 0x7E23 | 4 B     | GPIO4 Registers (USB-TIDE Data Reg)        |

| 0x7E1C | 0x7E1F | 4 B     | GPIO3 Registers (Left 7-Segment)           |

| 0x7E18 | 0x7E1B | 4 B     | GPIO2 Registers (Right 7-Segment)          |

| 0x7E14 | 0x7E17 | 4 B     | GPIO1 Registers (Parallel TIDE Port)       |

| 0x7E10 | 0x7E13 | 4 B     | GPIO0 Registers (Parallel TIDE Port)       |

| 0x7E00 | 0x7E0F | 16 B    | Hardware Breakpoint Registers              |

| 0x0200 | 0x7DFF | 31744 B | 31744 Byte Internal USER SRAM              |

| 0x0100 | 0x01FF | 256 B   | Stack Page Memory                          |

| 0x0000 | 0x00FF | 256 B   | Zero Page Memory                           |

### 2 MODULE DESCRIPTIONS

### 2.1 W65C02SRTL MODULE

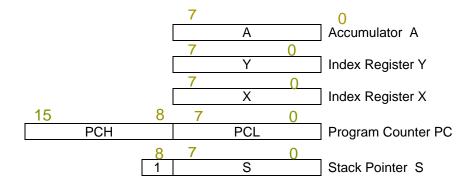

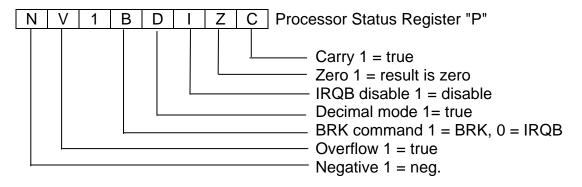

The W65C02S Microprocessor Programming Model, Status Register Coding, and Vector Table, are shown below. Please refer to WDC's W65C02S datasheet for complete information.

Figure 2.3.1 W65C02S Microprocessor Programming Model

Figure 2.3.2 W65C02S Status Register Coding

| Address | Label  | Function                                |

|---------|--------|-----------------------------------------|

| FFFF,E  | IRQBRK | BRK Vector High, Low                    |

| FFFD,C  | IRQRES | RES Vector High, Low                    |

| FFFB,A  | NMI    | Non-Maskable Interrupt Vector High, Low |

Table 2-5 Vector Table

### 2.2 GPIO MODULE

The General Purpose Input/Output (GPIO) Module is used to transfer information to and from the board using either WDC's embedded Terbium IDE (TIDE) monitor or custom IO software for control, test or debug purposes.

The Handshake Input (HSI) pin is used to handshake data into the GPIO port through the bi-directional 8 data pins. The Handshake Output (HSO) pin is used to handshake data output on the GPIO port data pins.

The 8 IO data pins can be set individually as inputs or outputs with the Data Direction Register (DDR) of the GPIO Module.

2.2.1 GPIO Module Register Descriptions

|           | ddress =<br>(1/2)3/7/B/F |        | STAT: GF                                           | PIO Control/S          | gister      | Reset Value = 0x02 |          |  |  |  |

|-----------|--------------------------|--------|----------------------------------------------------|------------------------|-------------|--------------------|----------|--|--|--|

| 7:0-<br>> | GIRQ                     | HIL    | HIE                                                | HIE TEST 0 0 HLOM HIES |             |                    |          |  |  |  |

| Bit       | Name                     | Access | Descript                                           | ion                    |             |                    |          |  |  |  |

| 7         | GIRQ                     | R/O    | 1 = GPIO Ir                                        | nterrupt Occurred      | (selected e | dge on HS          | I input) |  |  |  |

|           | Oliva                    | 100    | 0 = No GPI                                         | O Interrupt Occurr     | ed          |                    |          |  |  |  |

| 6         | HIL                      | R/O    | 1 = HSI Input Level high (DSR not ready)           |                        |             |                    |          |  |  |  |

| 0         | ПІС                      | R/O    | 0 = HSI Input Level low (DSR ready)                |                        |             |                    |          |  |  |  |

| 5         | HIE                      | R/W    | 1 = HSI Interrupt enabled (GIRQ Interrupt enabled) |                        |             |                    |          |  |  |  |

| 5         | HIE                      | K/VV   | 0 = HSI Interrupt not enabled                      |                        |             |                    |          |  |  |  |

| 4         | TEST                     | R/W    | 1 = Test with HSI connected to HSO                 |                        |             |                    |          |  |  |  |

| 4         | TEST                     | R/VV   | 0 = Normal mode                                    |                        |             |                    |          |  |  |  |

| 1         | HLOM                     | R/W    | 1 = HSO Le                                         | evel Output mode       | Set to high |                    |          |  |  |  |

| '         | HLOW                     | R/VV   | 0 = HSO Level Output mode to low (active)          |                        |             |                    |          |  |  |  |

|           | шгс                      | DAM    | 1 = HSI Interrupt Edge select set to Positive edge |                        |             |                    |          |  |  |  |

| 0         | HIES                     | R/W    | 1 = HSI Inte                                       | errupt Edge select     | set to Nega | ative edge         |          |  |  |  |

|       | dress =<br>1/2)2/6/A/E | GPIO_DDI | R: GPIO Data                                                          | Direction                     | Reset Value = 0x00 |  |  |  |  |  |

|-------|------------------------|----------|-----------------------------------------------------------------------|-------------------------------|--------------------|--|--|--|--|--|

| 7:0-> | DDR7                   | DDR6     | DDR5                                                                  | DDR5 DDR4 DDR3 DDR2 DDR1 DDR0 |                    |  |  |  |  |  |

| Bit   | Name                   | Access   | Description                                                           | Description                   |                    |  |  |  |  |  |

| 7 0   | DDD[7:0]               | R/W      | 1 = PIO data direction set to Output (bit 7 for PIO7, bit 0 for PIO0) |                               |                    |  |  |  |  |  |

| 7 - 0 | DDR[7:0]               | R/VV     | 0 = PIO data direction set to Input (bit 7 for PIO7, bit 0 for PIO0)  |                               |                    |  |  |  |  |  |

|       | dress =<br>1/2)1/5/9/D | GPIO_PUE | R: GPIO | Reset Value = 0xFF |      |      |      |      |

|-------|------------------------|----------|---------|--------------------|------|------|------|------|

| 7:0-> | PUE7                   | PUE6     | PUE5    | PUE4               | PUE3 | PUE2 | PUE1 | PUE0 |

| Bit | Name             | Access | Description                                                  |

|-----|------------------|--------|--------------------------------------------------------------|

| 7 0 | DUE(7.01         | DAM    | 1 = Pull-up on PIO Enabled (bit 7 for PIO7, bit 0 for PIO0)  |

| /-0 | 7 - 0   PUE[7:0] | R/W    | 0 = Pull-up on PIO Disabled (bit 7 for PIO7, bit 0 for PIO0) |

|       | dress =<br>1/2)0/4/8/C | GPIO_DAT | A: GPIO Data Register                                                                          |                               |  |  | Reset Value = 0x00 |  |  |  |

|-------|------------------------|----------|------------------------------------------------------------------------------------------------|-------------------------------|--|--|--------------------|--|--|--|

| 7:0-> | PIO7                   | PIO6     | PIO5                                                                                           | PIO5 PIO4 PIO3 PIO2 PIO1 PIO0 |  |  |                    |  |  |  |

| Bit   | Name                   | Access   | Descrip                                                                                        | Description                   |  |  |                    |  |  |  |

| 7 - 0 | PIO[7:0]               | R/W      | 1 = PIO line is logic 1 (returns value of PIO line on read, sets value to assert PIO on write) |                               |  |  |                    |  |  |  |

| 7 - 0 | F10[7.0]               | IN/VV    | 0 = PIO line is logic 0 (returns value of PIO line on read, sets value to assert PIO on write) |                               |  |  |                    |  |  |  |

## 2.3 Hardware Breakpoint Module (HBM) Module

A Hardware Breakpoint Match pulls NMIB low. Address 0F is the Control Register. The monitor needs to write a "0" into the Control Register after a breakpoint has been read to clear it. Writing a "1" to Bit 7 will cause a manual NMI if the breakpoint is enabled.

| Address | RTL Label | Description                                     |

|---------|-----------|-------------------------------------------------|

| 0       | BRKREG0   | Address byte 0 (bits 0-7)                       |

| 1       | BRKREG1   | Address byte 1 (bits 8-15)                      |

| 2       | BRKREG2   | Address byte 2 (bits 16-23)                     |

| 3       | BRKREG3   | Address byte 3 (bits 24-31) Reserved            |

| 4       | DATREG0   | Data Compare Value byte 0 (bits 0-7)            |

| 5       | DATREG1   | Data Compare Value byte 1 (bits 8-15) Reserved  |

| 6       | DATREG2   | Data Compare Value byte 2 (bits 16-23) Reserved |

| 7       | DATREG3   | Data Compare Value byte 3 (bits 24-31) Reserved |

| 8       | Reserved  |                                                 |

| 9       | Reserved  |                                                 |

| A       | Reserved  |                                                 |

| В       | Reserved  |                                                 |

| C       | Reserved  |                                                 |

| D       | Reserved  |                                                 |

| E       | Reserved  |                                                 |

| F       | ICDCTRL   | ICD Control Register                            |

## W65C02SPMCU Datasheet

## 2.3.1 Hardware Breakpoint Module (HBM) Register Descriptions

| F         | Address =<br>0x7E0F | HBM_ICI | DCTRL: Ha                                                    | Reset Value = 0x00                                                                   |                 |                          |  |  |  |  |  |

|-----------|---------------------|---------|--------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------|--------------------------|--|--|--|--|--|

| 7:0-<br>> | BRK                 | 0       | 0                                                            | 0 0 MATCH DATAEN RWSEL BRKI                                                          |                 |                          |  |  |  |  |  |

| Bit       | Name                | Access  | Descripti                                                    | on                                                                                   |                 |                          |  |  |  |  |  |

| 7         | BRK                 | R/W     | 1 = Hardwar                                                  | e Break occu                                                                         | rred            |                          |  |  |  |  |  |

| ,         | DIXIX               | 17/ 77  | 0 = No Hard                                                  | 0 = No Hardware Break occurred                                                       |                 |                          |  |  |  |  |  |

| 3         | MATCH               | R/W     | 1 = Data breakpoint if DATAREG value matches bus value       |                                                                                      |                 |                          |  |  |  |  |  |

| 3         | WATCH               | FX/ VV  | 0 = Data breakpoint if DATAREG value doesn't match bus value |                                                                                      |                 |                          |  |  |  |  |  |

| 2         | DATAFN              | R/W     | 1 = Enable b                                                 | = Enable breakpoint on data bus and DATAREG match (or mismatch as selected by bit 3) |                 |                          |  |  |  |  |  |

| 2         | DATAEN              | R/VV    | 0 = Disable breakpoint on Data                               |                                                                                      |                 |                          |  |  |  |  |  |

| 1         | RWSEL               | R/W     | 1 = Data bre                                                 | akpoint on R                                                                         | ead data (in to | MPU)                     |  |  |  |  |  |

| ' '       | RWSEL               | R/VV    | 0 = Data breakpoint on Write data (out from MPU)             |                                                                                      |                 |                          |  |  |  |  |  |

|           | DDIZEN              | R/W     | 1 = Enable b                                                 | reakpoint on                                                                         | match with Ado  | dress in BRKREG register |  |  |  |  |  |

| 0         | BRKEN               | K/VV    | 0 = Disable                                                  | 0 = Disable Address breakpoint                                                       |                 |                          |  |  |  |  |  |

|                 | dress =<br>x7E04 | HBM_DA | TAREG: Hardware Data Match                                                    |                                     |  |  | Reset Value = 0x00 |  |  |

|-----------------|------------------|--------|-------------------------------------------------------------------------------|-------------------------------------|--|--|--------------------|--|--|

| 7:0->           | DVAL7            | DVAL6  | DVAL5                                                                         | DVAL5 DVAL4 DVAL3 DVAL2 DVAL1 DVAL0 |  |  |                    |  |  |

| Bit             | Name             | Access | Description                                                                   |                                     |  |  |                    |  |  |

| 7 0             | D)/// [7:0]      | R/W    | Value of Data bus to match or mismatch with (as selected by ICDCTRL register) |                                     |  |  |                    |  |  |

| 7 - 0 DVAL[7:0] |                  | FK/VV  | bits 7-0 correspond to MPU data bus signals 7-0 for matching or not-matching  |                                     |  |  |                    |  |  |

|       | ldress =<br>x7E01 | HBM_BRK<br>Byte) | <u></u>                                                           |                                   | Reset Value =<br>0x00 |  |  |  |  |  |

|-------|-------------------|------------------|-------------------------------------------------------------------|-----------------------------------|-----------------------|--|--|--|--|--|

| 7:0-> | BADR15            | BADR14           | BADR13                                                            | BADR13 BADR12 BADR11 BADR10 BADR9 |                       |  |  |  |  |  |

| Bit   | Name              | Access           | Description                                                       | Description                       |                       |  |  |  |  |  |

| 7 - 0 | 0 0000115 01      | R/W              | Value of Address bus to match with                                |                                   |                       |  |  |  |  |  |

| 7-0   | BADR[15:8]        |                  | bits 15-0 correspond to MPU address bus signals 15-0 for matching |                                   |                       |  |  |  |  |  |

| Address = 0x7E00 |           | HBM_BR<br>Byte) | RKREG_L: H                                                        | Reset Value = 0x00 |  |  |  |  |  |  |

|------------------|-----------|-----------------|-------------------------------------------------------------------|--------------------|--|--|--|--|--|--|

| 7:0-<br>>        | BADR7     | BADR6           | BADR5 BADR4 BADR3 BADR2 BADR1 BADR                                |                    |  |  |  |  |  |  |

| Bit              | Name      | Access          | Description                                                       |                    |  |  |  |  |  |  |

| 7 -              | DADD[7:0] | R/W             | Value of Address bus to match with                                |                    |  |  |  |  |  |  |

| 0                | BADR[7:0] |                 | bits 15-0 correspond to MPU address bus signals 15-0 for matching |                    |  |  |  |  |  |  |

### 2.4 USBGPIO Interface for USB TIDE Port

USB interface for use with TIDE and WDC-DB PC software on the Terbi board. This module interfaces with the FTDI 245R chip. This interface uses 2 GPIO modules. The GPIO Data Register is described below for both GPIO Ports.

## 2.4.1 USBGPIO Module Register Descriptions

| 0x7E24 |        | GPIO5 Data - TIDE USB Status and Control Register |                                                               |  |  |  |

|--------|--------|---------------------------------------------------|---------------------------------------------------------------|--|--|--|

| Bit    | Access | Bit Name                                          | Description                                                   |  |  |  |

| 7      | R/O    | TxEmpty_B                                         | If set, then data register can be written to                  |  |  |  |

| 6      | R/O    | RxFull_B                                          | If set low, then data register contains valid data to be read |  |  |  |

| 5      | R/W    | ReadStrobe_B                                      | Read pulse out to the USBFIFO                                 |  |  |  |

| 4      | R/O    | Reset_B                                           | If set, then normal mode, if clear, then ESC-ESC rx'ed        |  |  |  |

| 3      | R/O    | PowerEnable_B                                     | If set, then FTDI chip finished USB enumeration               |  |  |  |

| 2-0    | -      | -                                                 | Not Used                                                      |  |  |  |

| Address =<br>0x7E(1/2)3/7/B/F |      | GPIO_CTRL_STAT: GPIO Control/Status Register |                                                          |  |      |      |  | Reset Value = 0x02 |  |  |

|-------------------------------|------|----------------------------------------------|----------------------------------------------------------|--|------|------|--|--------------------|--|--|

| 7:0-<br>>                     | GIRQ | HIL                                          | HIE TEST 0 0                                             |  | HLOM | HIES |  |                    |  |  |

| Bit                           | Name | Access                                       | Description                                              |  |      |      |  |                    |  |  |

| 7                             | GIRQ | R/O                                          | 1 = GPIO Interrupt Occurred (selected edge on HSI input) |  |      |      |  |                    |  |  |

|                               | Onto |                                              | 0 = No GPIO Interrupt Occurred                           |  |      |      |  |                    |  |  |

| 6                             | HIL  | R/O                                          | 1 = HSI Input Level high (DSR not ready)                 |  |      |      |  |                    |  |  |

| 0                             | ПІС  | R/O                                          | 0 = HSI Input Level low (DSR ready)                      |  |      |      |  |                    |  |  |

| 5                             | HIE  | R/W                                          | 1 = HSI Interrupt enabled (GIRQ Interrupt enabled)       |  |      |      |  |                    |  |  |

| 3                             |      |                                              | 0 = HSI Interrupt not enabled                            |  |      |      |  |                    |  |  |

| 4                             | TEST | R/W                                          | 1 = Test with HSI connected to HSO                       |  |      |      |  |                    |  |  |

| 4                             |      | r./ V V                                      | 0 = Normal mode                                          |  |      |      |  |                    |  |  |

| 1                             | HLOM | DAM                                          | 1 = HSO Level Output mode Set to high                    |  |      |      |  |                    |  |  |

|                               |      | R/W                                          | 0 = HSO Level Output mode to low (active)                |  |      |      |  |                    |  |  |

|                               | HIES | DAM                                          | 1 = HSI Interrupt Edge select set to Positive edge       |  |      |      |  |                    |  |  |

| 0                             |      | R/W                                          | 1 = HSI Interrupt Edge select set to Negative edge       |  |      |      |  |                    |  |  |

## W65C02SPMCU Datasheet

|       | dress =<br>x7E20 | GPIO_DAT | A: TIDE (                     | JSB Data F                          | Reset Value = 0x00 |  |  |  |  |

|-------|------------------|----------|-------------------------------|-------------------------------------|--------------------|--|--|--|--|

| 7:0-> | DATA7            | DATA6    | DATA5                         | DATA5 DATA4 DATA3 DATA2 DATA1 DATA0 |                    |  |  |  |  |

| Bit   | Name             | Access   | Description                   |                                     |                    |  |  |  |  |

| 7 - 0 | DATA             | R/W      | RX (read) and TX (write) Data |                                     |                    |  |  |  |  |